Xilinx ZYNQ UltraScale+系列连载[第三篇]写一篇简单需求

作者:hello,panda

离上篇博客发布已经有很长的时间了,请原谅楼主,一个是小Panda降临需要照顾,另一个是确实这段时间的工作太忙,拖到今天才开始动笔写第三篇。

做事情讲究个“谋定而后动”,做研发尤其如此,准备工作一定要做得充分了,需求一定要理解明确了,方可开始吭哧吭哧继续往下干。

楼主先准备以ZCU104为平台,实现一个视频处理和传输系统,算是熟悉ZYNQ UltraScale+ MPSoC器件。

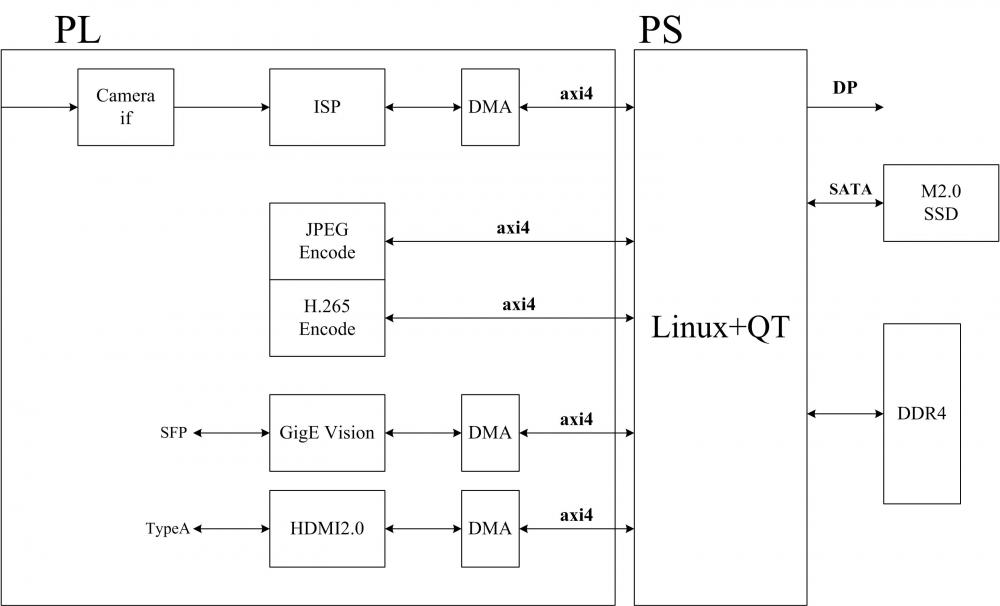

总体要求是:设计一个图像采集、处理和传输系统,实时视频分辨率不小于4000×3000,帧率不小于30fps,视频可通过HDMI2.0(或DP)接口本地实时显示。JPEG压缩的图片和H.265压缩后的视频存储在本地SATA盘中,实时码流可通过GigE Vision传输到主机。系统总体框架如下图1所示。

图1 系统总体框架

1 硬件平台

本阶段先使用ZCU104平台进行验证,Camera和SFP接口通过FMC扩展板实现。

2 软件需求

软件包括PL和PS两个部分,其中PL部分实现Camera IF、ISP、Encoder、GigE Vision和HDMI2.0接口;PL部分运行Linux操作系统,使用QT图形界面,驱动DP显示和SSD存储。

2.1 PL部分

PL部分主要实现接口和算法。

2.1.1 相机接口(Camera IF)

Camera IF硬件上通过FMC接口板接入,支持LVDS(LVDS通道数不大于15对)、MIPI D-PHY、MIPI C-PHY接入。Camera 分辨率不低于4000×3000,帧率不低于30fps,8bit、10bit或12bit Raw(Bayer)数据输入。

2.1.2 图像信号处理(ISP)

本阶段ISP实现基本功能,主要包括:Demosaic、CCM、3A、Dpc、Gamma、Denoise、Enhance等基本内容,ISP需保证对输入图像实时处理。

2.1.3 Encoder

Encoder主要有两部分,一个H.265视频流压缩,一个是JPEG静态图片压缩。H.265使用芯片内置的硬核,JPEG压缩通过逻辑实现。H.265至少保证4000×3000分辨率30fps实时压缩。

2.1.4 GigE Vision网络传输

GigE Vision采用10G光口传输,硬件在FMC扩展板上实现。GigE Vision可实时传输原始图像、ISP处理后的图像、H.265码流和JPEG静态图片,通过xml配置文件指定支持的源和格式。

2.1.5 HDMI2.0接口

基于GTH,符合HDMI2.0标准,显示原图或ISP后的图像,可叠加OSD。

2.2 PS部分

PS部分运行Linux操作系统,运行QT叠加生成OSD。

2.2.1 调度功能

PS需配置PL工作的各项参数,获取系统状态,运行3A算法的C部分。PS部分还需处理PL的各中断,以协同处理存储、显示等工作。

2.2.2 存储和显示

实现DP和SATA驱动,存储和读出PL生成的视频流文件请求。运行QT,生成人机交互界面。

3总结

整个系统基于AXI4总线架构,SoC软件硬件协同处理,需要保证良好的可扩展性,以便扩展下一步的图像检测和识别算法、AI算法等。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。