(Fluke TiX1000红外热像仪)

本文作者:Hello,Panda

基于非制冷探测器的红外测量系统可在各领域广泛应用。如海关、机场等公共场所民众体温监测,芯片、焊点、激光光纤等微米级目标检查,高压输电塔巡线,隧道、大坝、桥梁渗水检测,反应塔、高炉等大型工业设备维护,建筑缺陷检测、地质勘探、火山研究,生命科学和化学研究等等。为便于描述,本文即以非制冷系统为例聊一聊ZYNQ-7000器件(制冷的当然也可以,但是属于特殊小众,不便展开)的应用。

1.引子

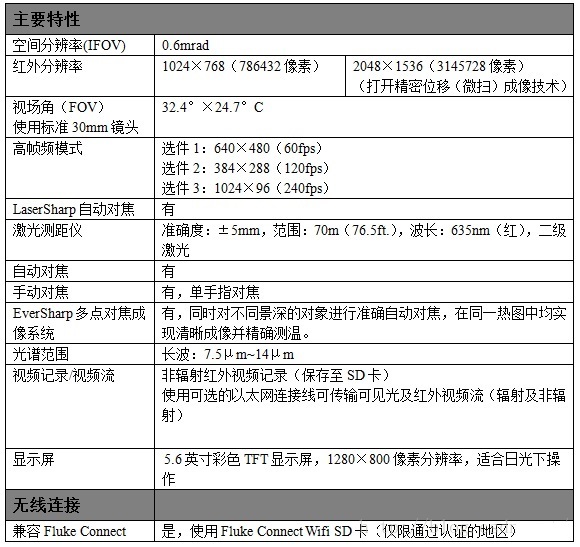

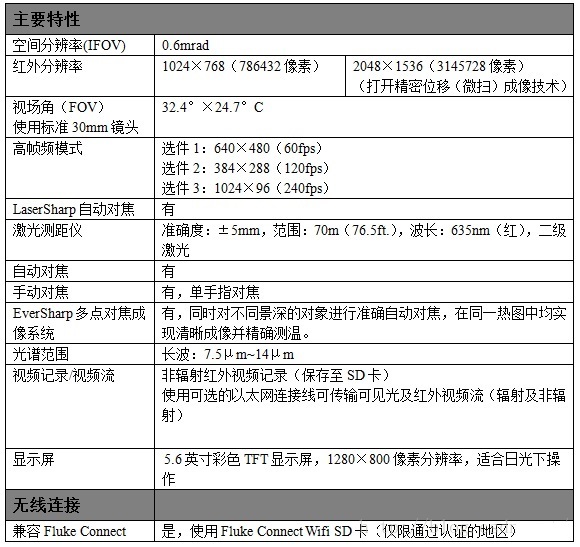

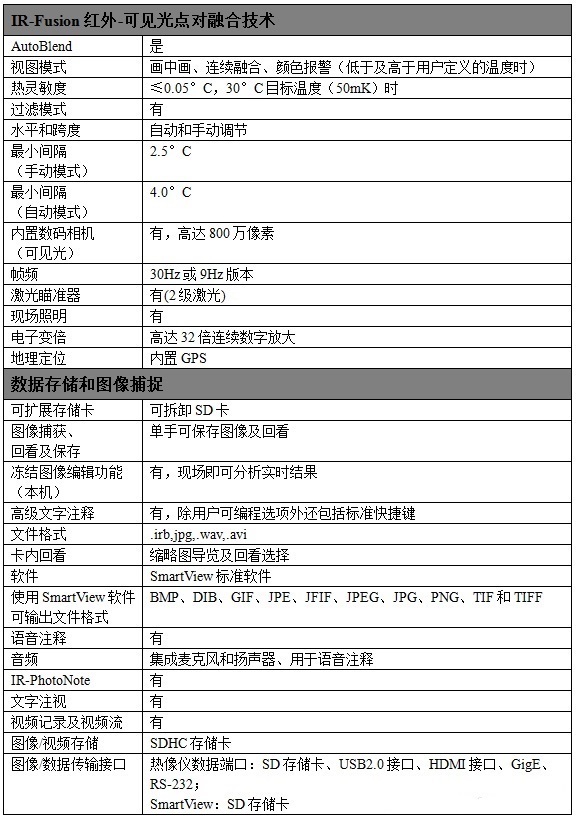

在进一步展开说明之前,我们先看一组业内标杆Fluke生产的便携式红外热像仪TiX1000的相关指标,如下表1所示。

表1 FlukeTiX1000红外热像仪系统指标

根据表1 Fluke TiX1000红外热像仪,可以看到测量类红外图像系统呈现以下发展趋势:

① 高分辨率和高帧率:

a) 探测器像素可达1024×768甚至更高;

b) 紧密位移成像技术(微扫)可输出四倍有效像素;

c)为满足高速测量要求,可对探测器“开窗”实现高帧率图像输出;

② 多光谱图像融合:和高分辨率CCD\CMOS等可见光图像融合;

③ 更宽测量范围和更高测温精度;

④ 激光测距辅助精准对焦;

⑤ 更丰富接口满足远程测量、分布式测量和图像存储等功能;

⑥ 配件可更换:和数码相机一样,可以根据不同的应用需求更换镜头;

⑦ 更加便携和更低功耗。

多元化的功能,低功耗,特别适合使用ZYNQ-7000器件实现。

2 .设计考虑的关键因素

参照Fluke的技术指标,影响设计的关键点是:

①高分辨率红外、可见光图像处理和融合;

②图像压缩、传输;

③精准测温、精准自动对焦;

④重量、体积和电池续航时间;

在传统的设计里,红外图像和可见光图像通常经过不同的模组进行预处理,然后再进行融合。这种传统方式的显著缺点是电路复杂,电路板(模组)多,功耗大。既导致了电池续航能力短,又增加了整机的重量和体积,同时可靠性也大打折扣。

那么,有没有一种解决方案可以在单片内有能力完成所有的处理(大量数据处理和高带宽要求),可以显著降低面积和功耗呢?不用怀疑,当前两大FPGA厂商Altera和Xilinx提供的的Cyclone V和ZYNQ-7000系列SoC都可以做到。

两大巨头的SoC都集成了双核Cortex-A9 ARM处理器、可编程逻辑和丰富的外设。软硬件协同处理、完美结合,正符合多光融合的非制冷红外测量系统的应用特点。

在熊猫君的这个例子里面,以Xilinx ZYNQ SoC为例,提供一种设计思路。

3.硬件设计思路

硬件设计的关键是①选用有足够计算资源的器件;②提供足够的缓存和存储带宽;③满足要求的外设接口和I/O资源;④高效率电源系统。

3.1 计算资源考虑

这里的计算资源是一个泛指,包括对可编程逻辑资源和ARM端处理资源的要求。

3.1.1 可编程逻辑资源

可编程逻辑资源消耗分布如下:

① 红外图像处理:包括非均匀性校正、盲元校正、测温模块、降噪与增强、直方图均衡、(IDE)、微扫描图像合成、(宽动态强化高温区和低温区细节)、伪彩色映射、Zoom等;

② 可见光图像处理:ISP、降噪与增强、(宽动态技术)等;

③ 图像融合:红外图像和可见光图像融合;

④ 图像压缩:红外灰度图像特点,一般采用MJPEG压缩保留较多细节和较低延时。

⑤ 显示和接口:OSD图层、Scaler、HDMI接口、LVDS或MIPI CMOS输入接口、ONFI NAND接口、DDR Mig、和PS及DDR交互的AXI DMA等;

⑥自动对焦:梯度或锐度、模糊度计算。

按照一般的思路,没有过于复杂的如神经网络之类的算法,在架构清晰、代码风格比较好的情况下,XC7Z020(85K逻辑)可满足设计要求。如果需要添加更加复杂的检测、识别、跟踪类算法,可考虑选用XC7Z030(125K逻辑),当然器件成本会成倍上升。

3.1.2 缓存带宽资源

一幅红外图像的像素个数是1024×768,一幅可见光图像的像素个数为3840×2160。根据不同情况,一个像素可能占一个或两个字节,标准帧率为30fps,在精确位移打开或宽动态打开的情况下最终输出的帧率会降低,带宽不会成四倍增加。

缓存主要产生于数据处理过程中的DDR缓存,红外、可见光、压缩处理一帧和DDR的数据交互约在6~12次之间,按每像素2字节计算,那么所需要的总带宽可能高达:

((1024*768)+(3840*2160))*2*30 *12= 6.1GB/s

同时,PS运行的ARM代码、千兆网接口、GUI均要消耗一定的带宽资源。

显然单靠PS端的DDR带宽无法满足,因此在PL端需要扩展DDR存储器。

3.1.3 外设接口和I/O资源

外设接口主要包括GigE、USB、SDIO/SDHC、IIC、SPI、UART、QSPI、HDMI、NAND、LVDS(或MIPI)、PPI、I/O量等。前6项在PS端有控制器、后四项需要占用FPGA端I/O,使用CLG484及以上封装器件肯定不会存在Less I/O的问题。

3.2 硬件框图

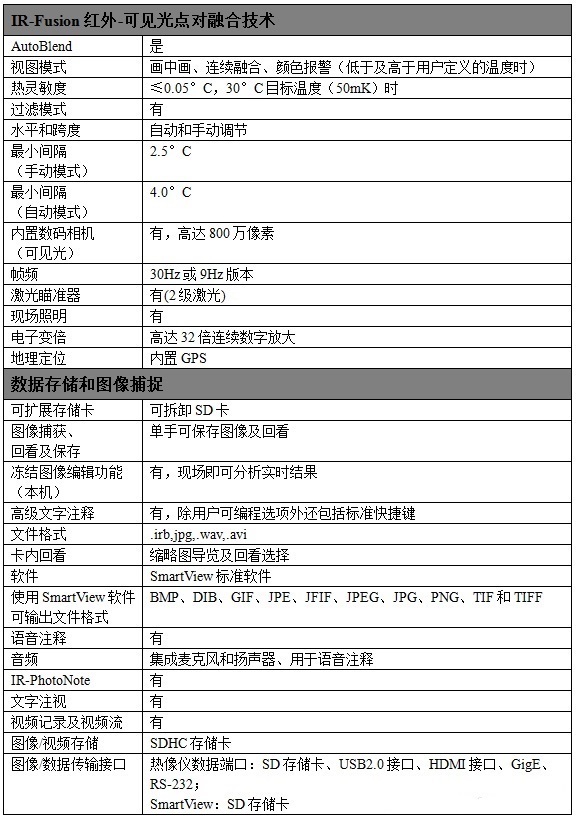

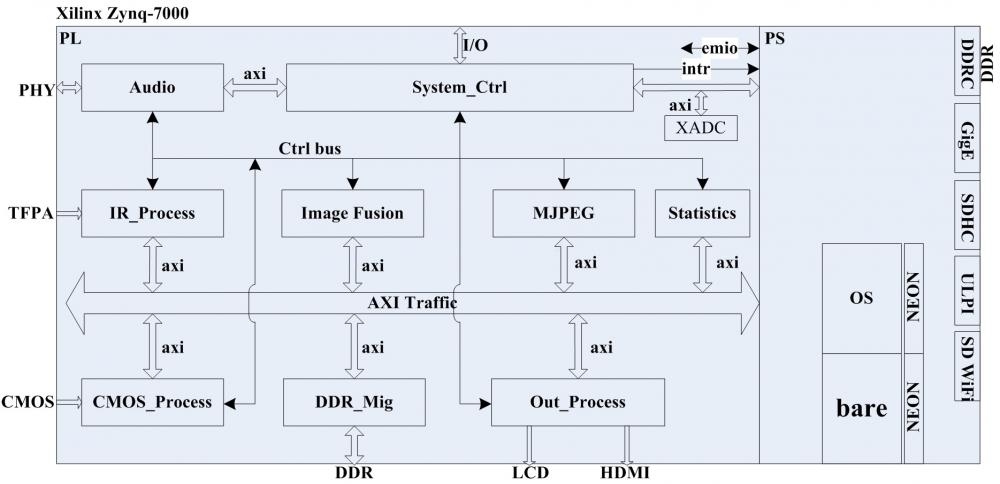

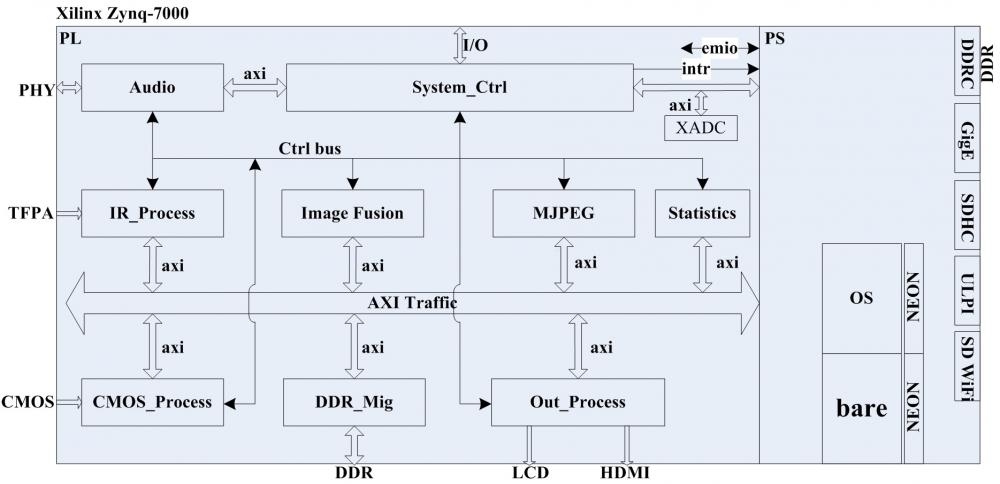

总结起来,本例所描述的硬件系统框图如下图1所示。

图1 系统硬件框图

如图1所示,系统为基于Xilinx ZYNQ-7000的单处理器解决方案,左边淡紫色部分是可编程逻辑,接入CMOS、红外焦平面图像数据,LCD和HDMI显示接口,NAND Flash存储接口,DDR Mig以及其他的相关外设等。PS端主要是GiE、USB ULPI、SDIO等标准接口,由PS内的相关控制器管理。

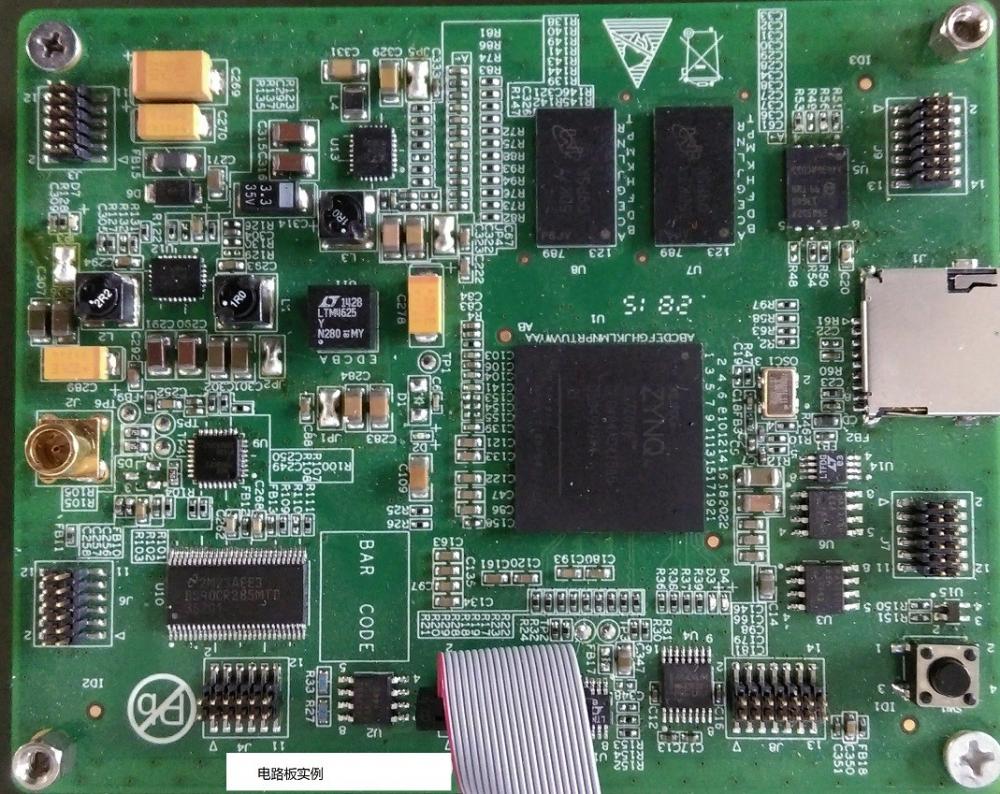

4. 软件设计思路 软件包含PS端运行的软件和PL端的可编程逻辑。整个软件系统的结构如下图2所示。

PS端的双核ARM其中一个核运行操作系统(OS),另外一个核运行裸机程序(Bare)。运行操作系统的核主要负责外设驱动管理、系统控制、应用管理、GUI等功能。运行裸机代码的核和NEON一起主要偏重算法辅助处理。

软件镜像和可编程逻辑bit文件存储在PS端挂载的QSPI Flash上。

4.2 PL端软件

PL端软件遵循模块化设计的原则,数据流采用标准的AXI总线标准传输。主要的处理单元分为以下主要模块。

(1)IR_Process:红外图像处理,包括非均匀性校正、盲元校正、测温模块、降噪与增强、直方图均衡、(IDE)、(宽动态强化高温区和低温区细节)、伪彩色映射、Zoom等;(微扫描图像合成只是简单的将四幅图拼成一幅图,纯DDR取数操作)。

(2)CMOS_Process:CMOS可见光处理,包括基本的ISP(Demosaic、Auto WB、CCM、DpC、Gamma等)、3D降噪与增强、可选的HDR Tone Mapping功能。

(3)Out_Process:输出和显示处理,包括Scaler、OSD及对应的显示接口逻辑等。

(4)Image Fusion:可选模块,可见光与红外图像融合。

(5)MJPEG:JPEG编码,可同时实时编码红外和可见光图像。PS端将码流封装成图片和avi视频流。为满足实时性,这里采用5个MJPEG编码模块(默认红外1个,可见光4个同时编码),可单独编码红外、可见光、红外可见光融合后的图像以及带温度注释、语音注释的图像。

(6)Statistics:数据统计,3A(自动曝光(自动积分调整)、自动白平衡、自动对焦)数据统计,结果实时更新到PS决策。

(7)Audio:可选的语音处理模块,包含用于语音注释的语音识别功能(调用第三方库数据)。

(8)System_Ctrl:系统中央控制单元,调度各模块的Frame Buffer、配置各模块工作参数、对GPS、黑体、电机等I/O量进行采集和控制。

5.总结

本例仅仅描述了在Zynq-7000器件上实现的方案级框架型设计概要,当然该方案也可以在Xilinx最新的Zynq UltraScale+ MPSoC(集成了HEVC和GPU)上实现,开发周期更短、性能更高,代价是需要付出更高的BOM成本。感兴趣的同行可加入讨论群300148644进行进一步技术交流。

(原创文章,转载请注明出处)

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。